Further discussion with Peter:

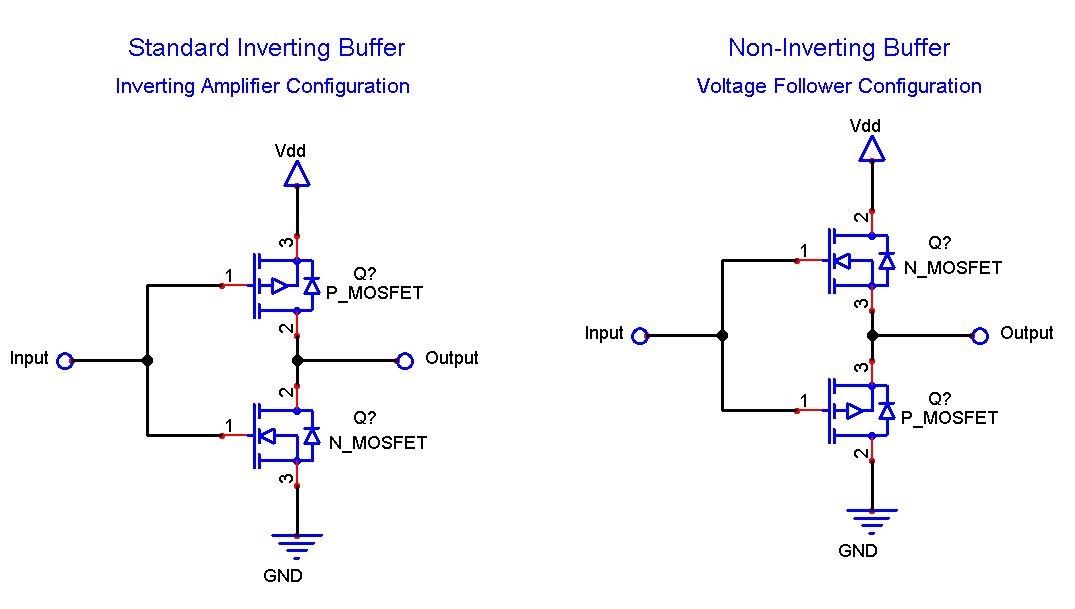

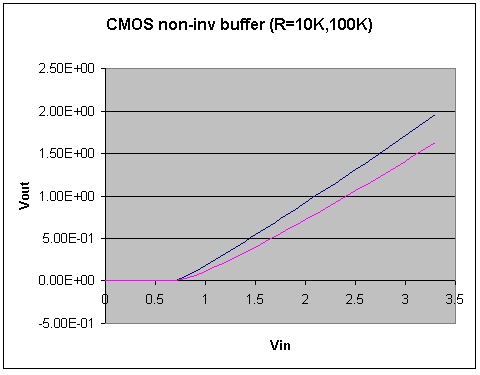

> > This configuration will indeed work as a current regulated noninverting buffer. The assumption that both transistors will be in cut-off is incorrect. A high will place the upper MOSFET in a standard current source configuration and a low will make the lower MOSFET a current sink. The output will function as a current sink or source depending on the input. It is quite safe to assume that the gate threshold for transistors in a CMOS device will be well below 1/2 Vcc when they are required to be near saturation at 2/3 Vcc. The output swing will be reduced by the gate threshold level (likely around 0.8V from either supply rail with no load and having good current regulation for voltages greater than 2V from rail). It will not meet CMOS output specifications but it will be a noninverting “soft” buffer.

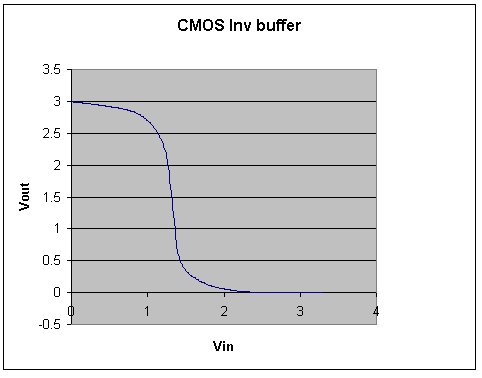

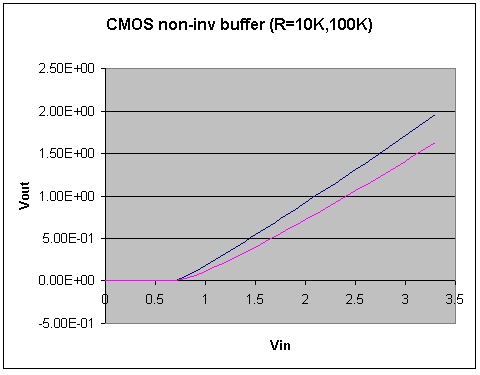

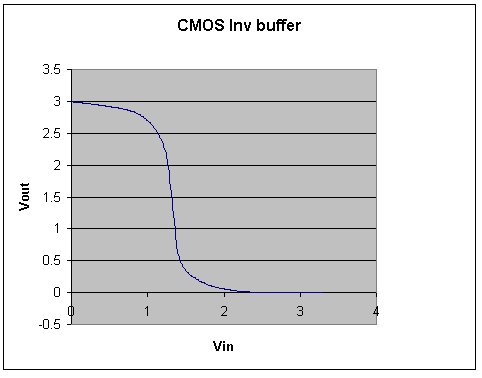

------------------- >Alex wrote: >I agree with you that the assumtion of both transistors being in cut- >off mode (Inverting buffer question) may be incorrect. Spice tells they >can sink/source some current , but the circuit can't work as a non- >inverting buffer, not even a "soft" one. ------------------- >Peter: > I must differ with you on this question however. >The output of a CMOS buffer that has the P-channel and N-channel >transistors swapped will be a non-inverting buffer with the output >voltage limited from reaching either supply rail by the gate threshold >voltage. Each transistor will be in a follower configuration rather than >being an inverting amplifier. >I was mistaken about the current limiting aspect. I was thinking of >J-FETs in that configuration but MOSFETs will provide full output >current. I assembled the circuit just to measure the actual performance >and it does function. I didn't have any logic level TO-92 MOSFETs so the >minimum supply voltage was around 6 volts but it does work just fine. >Thank you for responding. I appreciate the dialog but again there is no >urgency on hypothetical situations. ----------------------- >Alex: >Below there are Spice setup files and simulation results (Vin/Vout plots) for both inverting and non-inverting buffers. The plots show that the non-inverting circuit can sink and source some current, but doesn't have the sharp switching charachteristic like an inverting buffer. Peter's empiric results, however, tell the non-inverting buffer does work. Could be another mismatch between simulation and breadboard? We invite more comments from other people.

|

|

*CMOS INVERTER .MODEL NFET NMOS(LD=0.12u VT0=0.7) .MODEL PFET PMOS(LD=0.12u VT0=-0.7) Vdd 1 0 DC 3.3V Vin 2 0 DC 0V M1 1 2 3 1 pFET (L=2.2u W=91.3u) M2 3 2 0 0 nFET (L=2.2u W=91.3u) R1 3 0 10k .DC Vin 0V 3.3V 0.01V .PRINT DC V(3) .END |

*CMOS NON-INVERTER *P and N type devices swapped, bulk nodes connected to output .MODEL NFET NMOS(LD=0.12u VT0=0.7) .MODEL PFET PMOS(LD=0.12u VT0=-0.7) Vdd 1 0 DC 3.3V Vin 2 0 DC 0V M1 1 2 3 0 nFET (L=2.2u W=91.3u) M2 3 2 0 1 pFET (L=2.2u W=91.3u) R1 3 0 10k .DC Vin 0V 3.3V 0.1V .PRINT DC V(3) .END |